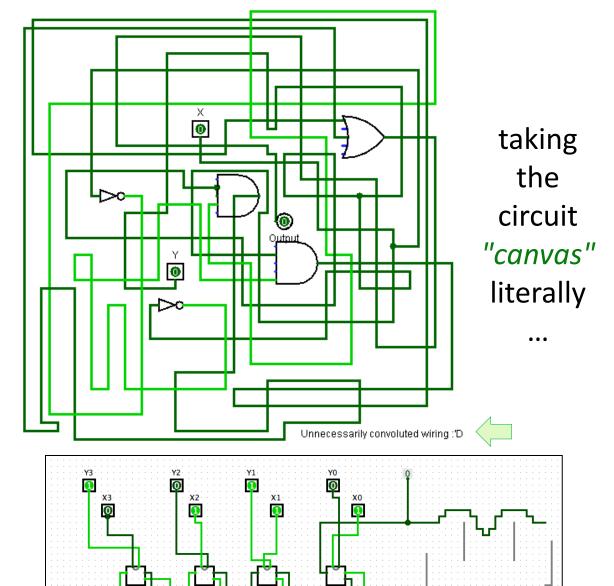

# CS 5 **Python** Hmmm... computer main memory registers 1-bit memory: flip-flops arithmetic Ν bitwise functions logic gates switches: transistors Things are awfully messy 'round here...

An example of a *happy*

Ripple-Carry Adder...

# hw5 ~ composing circuits

3-bit Full Adder

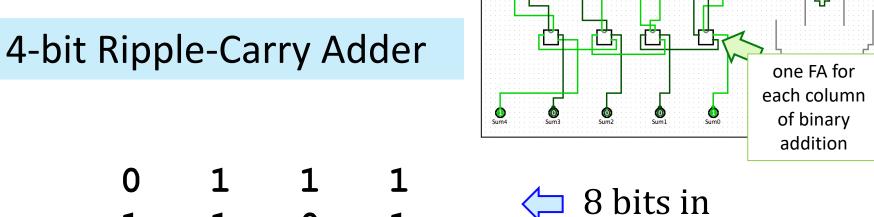

4-bit Ripple-Carry Adder

Prime tester

using "minterm expansion"

4-bit **Multiplier**

3x2-bit **Divider**

extra credit

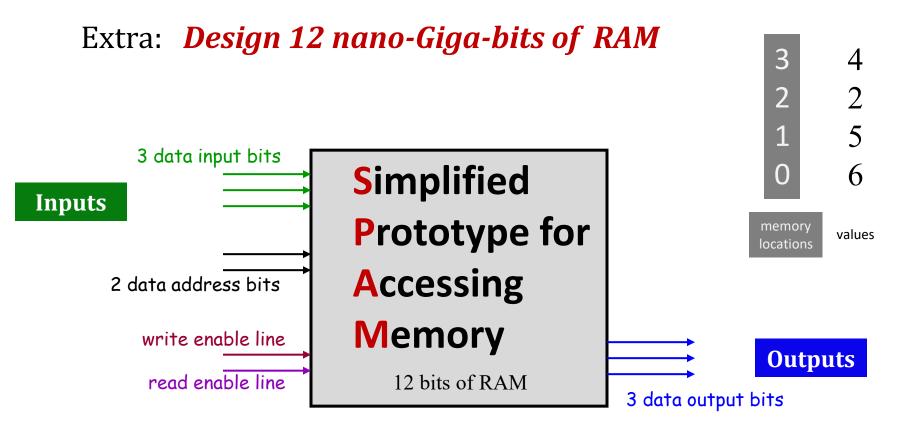

12 nGbits of memory (RAM)

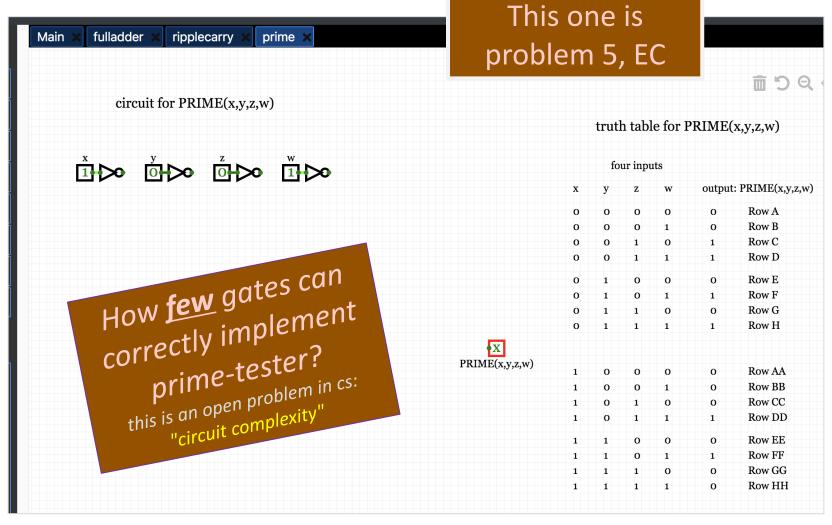

Optimized Prime

# Worst-case, so far...

# Worst-case, so far...

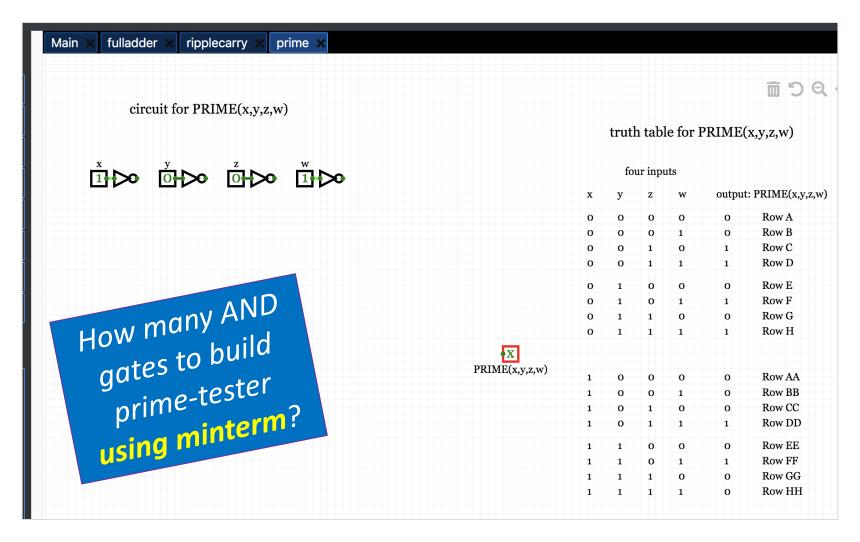

#### Prime-tester...

pure "minterm expansion": one <u>AND</u> for each <u>'1' output</u>

Prime-optimizer?!

pure "minterm expansion": one <u>AND</u> for each <u>'1' output</u>

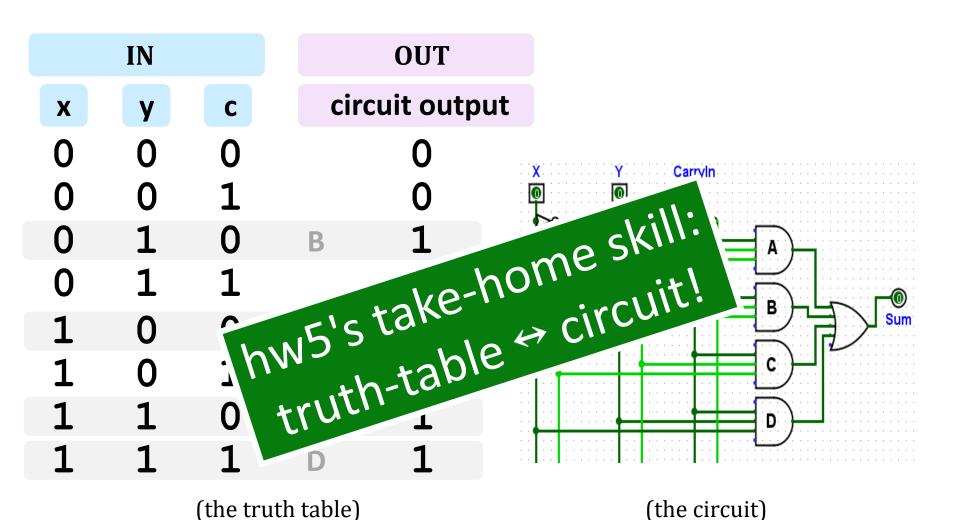

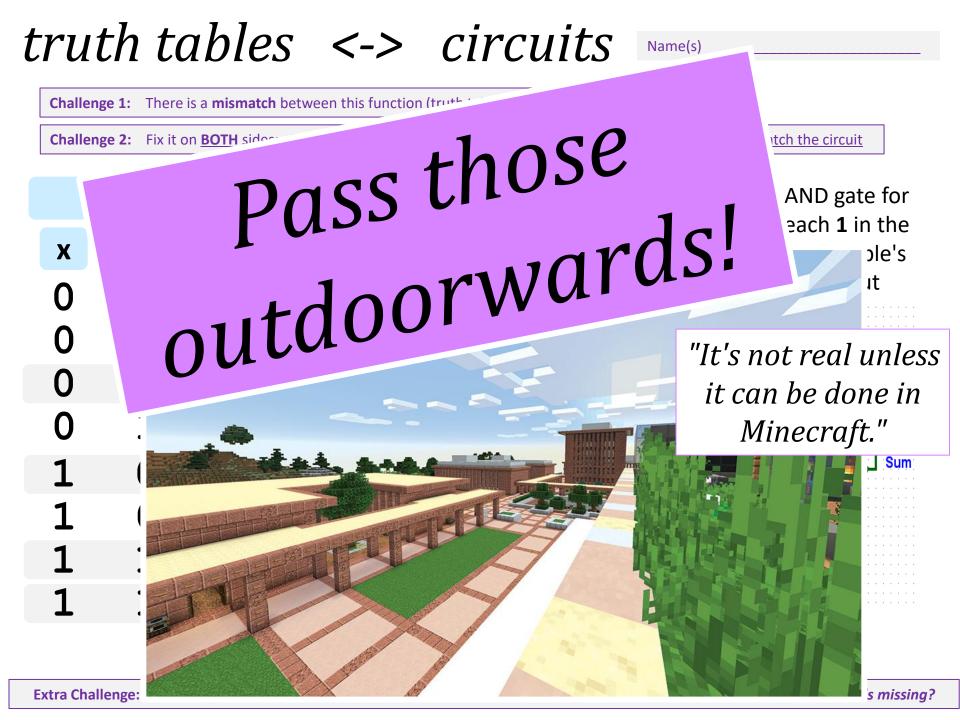

#### truth tables ↔ circuits

#### truth tables ↔ circuits

Name(s) \_\_\_\_\_

**Challenge 1:** There is a **mismatch** between this function (truth table) and circuit.

Challenge 2: Fix it on BOTH sides: Draw how to make the circuit match the table + how to make the table match the circuit

|                   | IN |   |      | OUT         | AND gate for each <b>1</b> in the |

|-------------------|----|---|------|-------------|-----------------------------------|

| X                 | y  | C | circ | cuit output | truth table's                     |

| 0                 | 0  | 0 |      | 0           | x ····· y ···· c                  |

| 0                 | 0  | 1 |      | 0           |                                   |

| 0                 | 1  | 0 | В    | 1           |                                   |

| 0                 | 1  | 1 |      | U           |                                   |

| 1                 | 0  | 0 | Α    |             | Sum                               |

| 1                 | 0  | 1 |      | 0           | <u>c</u> )                        |

| 1                 | 1  | 0 | C    | 1           | <b>D</b>                          |

| 1                 | 1  | 1 | D    |             |                                   |

| (the truth table) |    |   |      |             | (the circuit)                     |

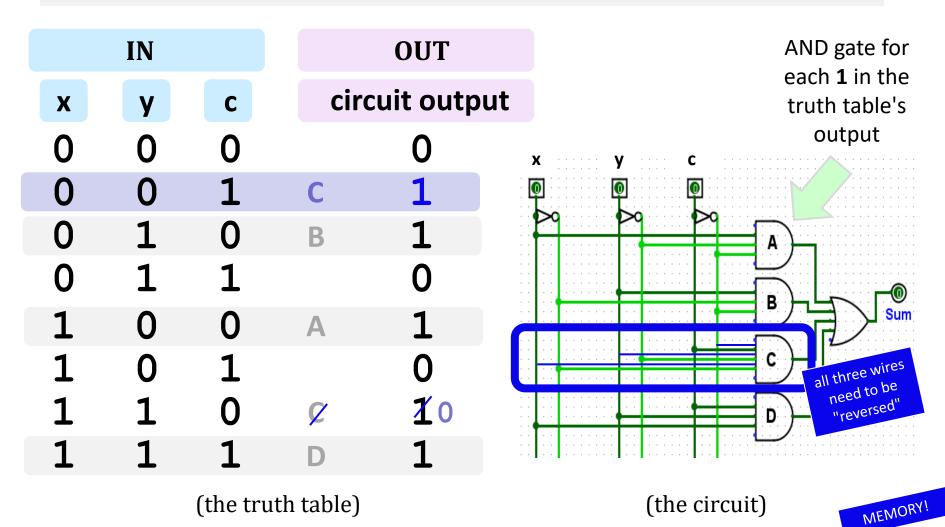

#### truth tables ↔ circuits

Try this on the other page first...

Row **6** (110) has no AND gate!

Row 1 (001) does have an AND gate!

**Challenge 1:** There is a **mismatch** between this function (truth table) and circuit.

Challenge 2: Fix it on BOTH sides: Draw how to make the circuit match the table + how to make the table match the circuit

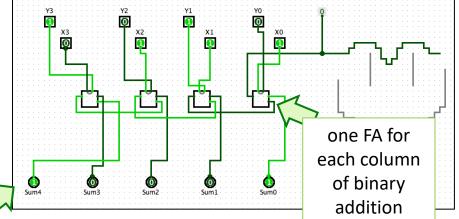

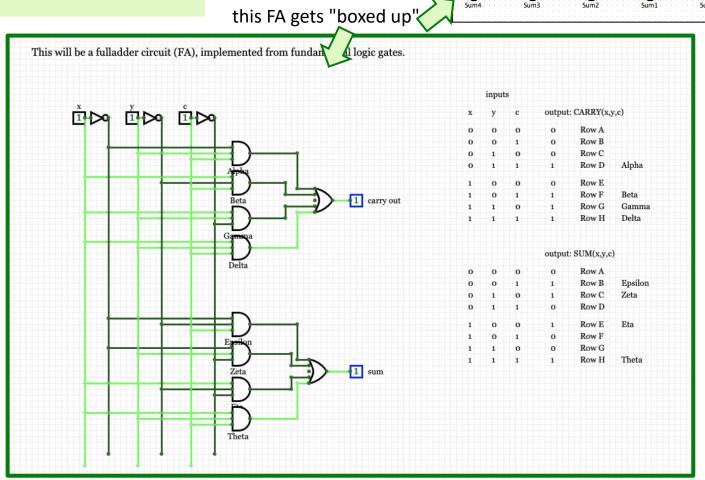

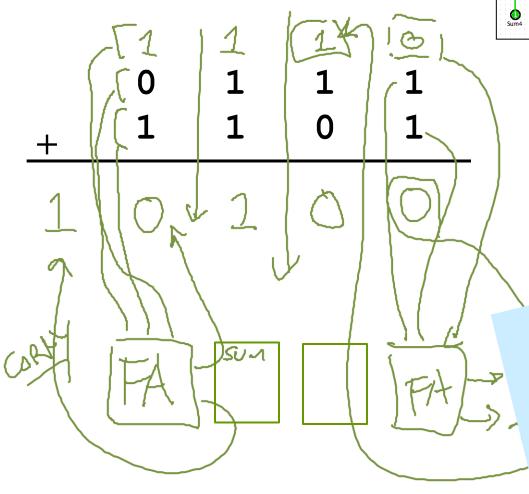

Full Adder ~ minterm

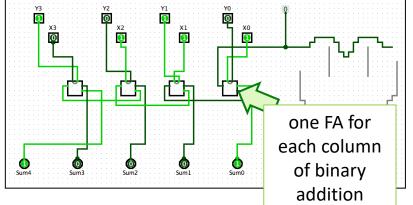

5 full adders

one FA for each column of binary addition

5 "sum" bits

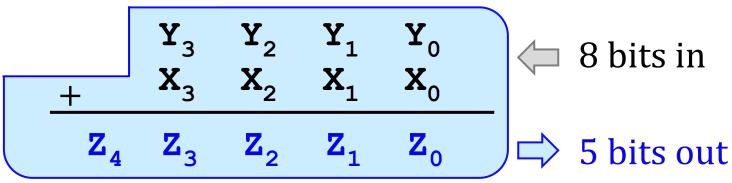

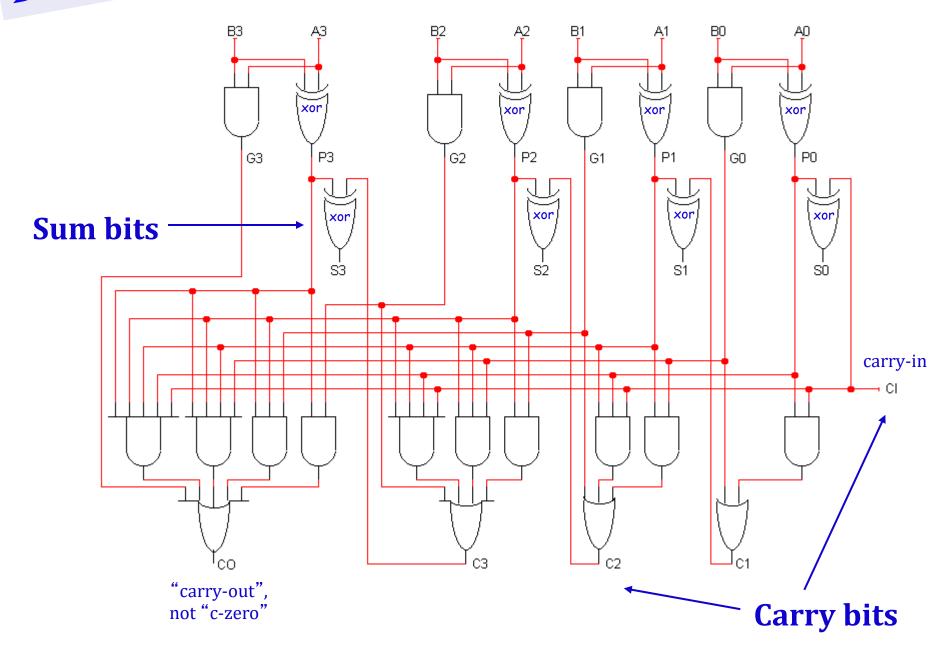

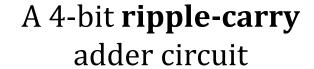

#### 4-bit Ripple-Carry Adder

- 8 bits in

let's abstract these details away...

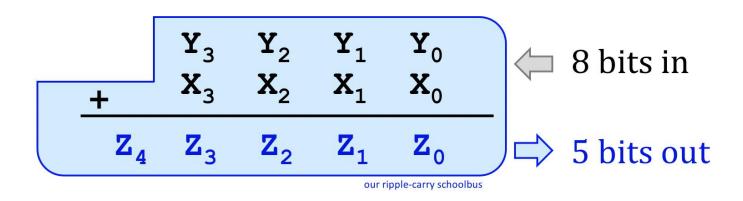

#### 4-bit Ripple-Carry Adder

keep abstracting!

#### 4-bit Ripple-Carry Adder

keep abstracting!

our ripple-carry schoolbus

a ripple-carry "bus"!

4-bit Ripple-Carry Adder

keep abstracting!

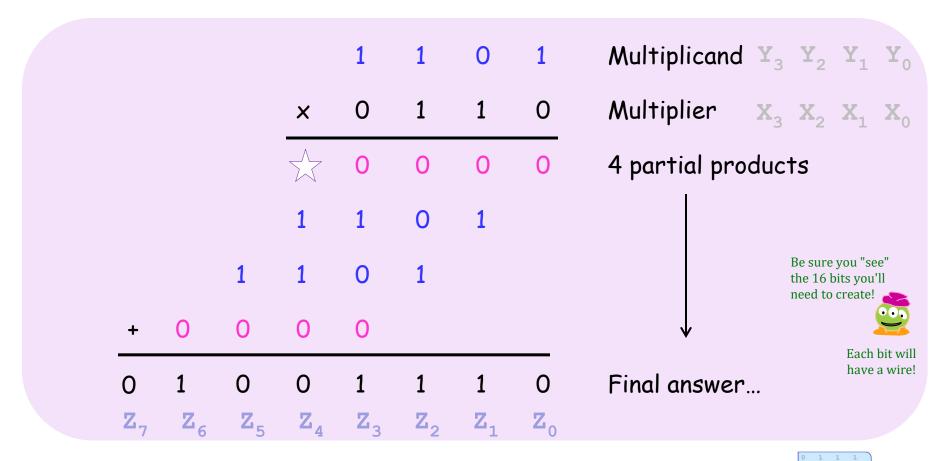

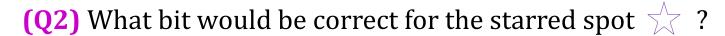

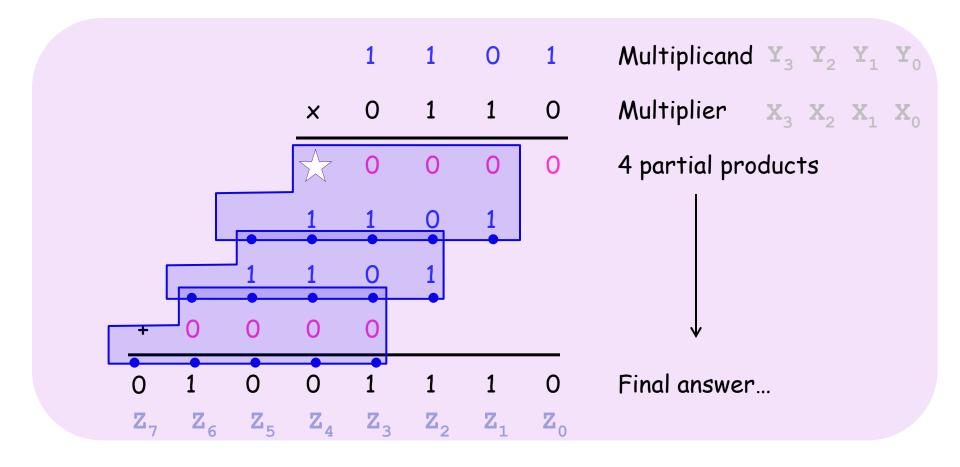

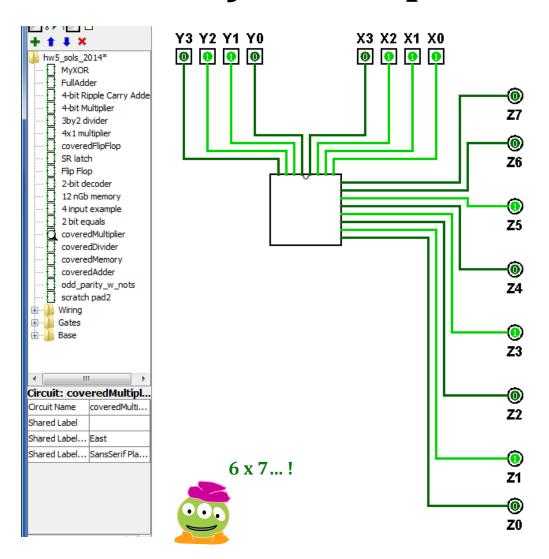

#### hw5pr3: A 4-bit multiplier

(Q3) How could **THREE** 4-bit ripple-carry adders help here?

(Q1) What circuit could you use to create the four "partial products"??

The Challenge...

#### hw5pr3: A 4-bit multiplier

(A1) The AND gate is *single-bit* multiplication.

$$(A2) \Rightarrow == 0$$

- (A1) Use a 4x1-bit helper circuit to find the four *partial products...*

- (A3) You need three (3) ripple-carry adders to finish: see above...

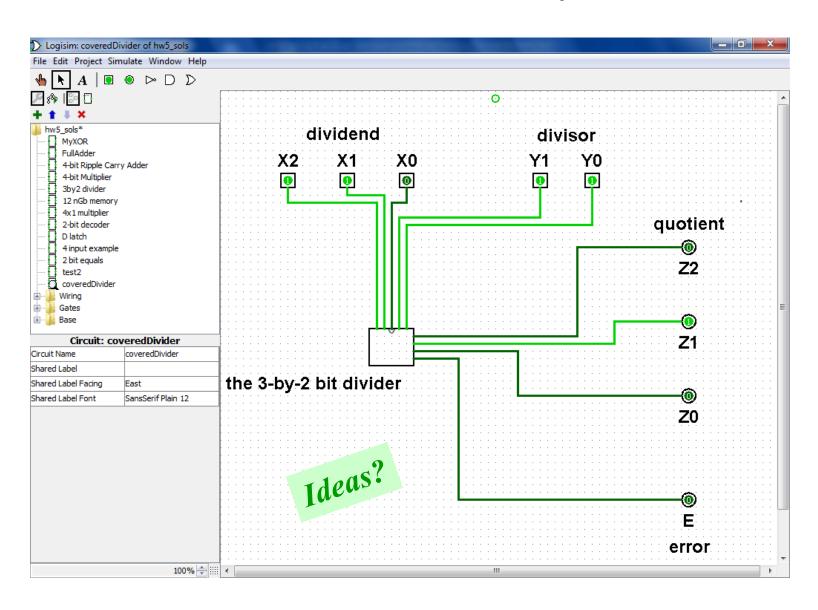

# Division? hw5pr4

# Division! hw5pr4

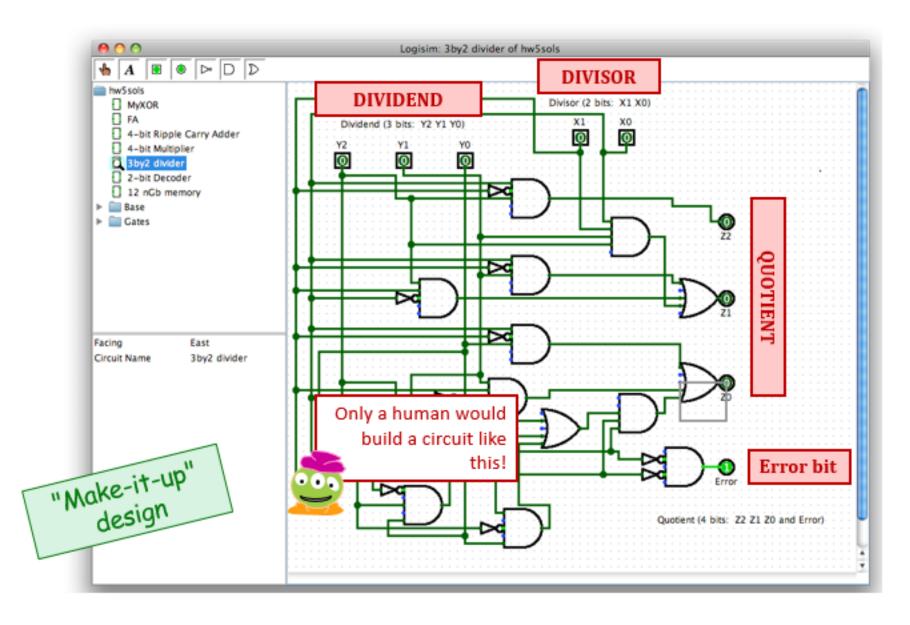

"principled" design

#### Minterm *Division*

**INPUTS**

OUTPUT

- dividend

- **Z2 Z1 Z0** auotient

- All computation can be expressed as bits...

- anything div. by 0

anything

- (1) *Any* function of bits can be made a truth table

(2) Consider the output, one bit at a time...

(3) The circuit will output 0 by default!

- (4) Are there *subcircuit patterns* to notice?

- (5) *If not*, use an AND gate to **select** each input

- for which the output should be 1 (a minterm!)

To implement the red 1, how many inputs will its AND gate need??

How many **NOT**'ed?

What division is that line?

- (6) OR the outputs from step (5) together.

- optimize your circuit later -- or never

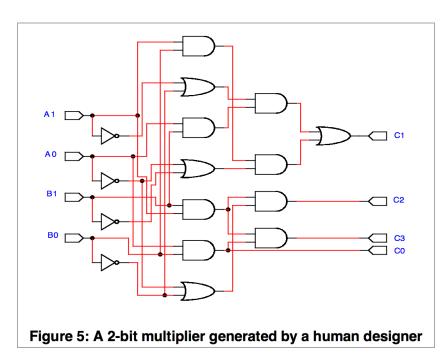

# Circuit *Optimization*?

Figure 7: A 2-bit multiplier generated by a GA using our approach

7 gates

16 gates

### Optimizing for what?!

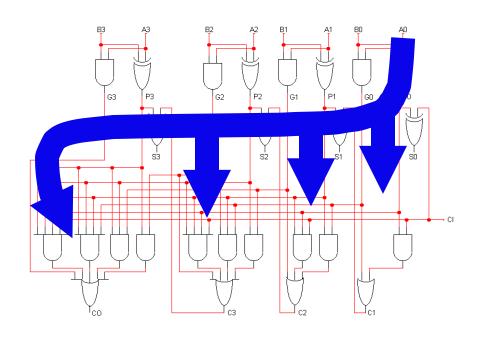

#### <u>Time</u>-optimized circuits: *Carry lookahead adders*

The following circuit is called a carry lookahead adder.

By adding more hardware, we reduce the number of levels in the circuit and speed things up.

We can "cascade" carry lookahead adders, just like ripple carry adders. We'd have to do carry lookahead between the adders too.

#### How much faster is this?

For a 4-bit adder, not much. There are 4 gates in the <u>longest path</u> of a carry lookahead adder, versus 9 gates for a ripple carry adder.

But if we do the cascading properly, a 16-bit carry lookahead adder could have only 8 gates in the longest path, as opposed to 33 for a ripple carry adder.

Newer CPUs these days use 64-bit adders. That's 12 vs. 129 gates or 10x speedup!

The delay of a carry lookahead adder grows *logarithmically* with the size of the adder, while a ripple carry adder's delay grows *linearly*.

The thing to remember about this is the **trade-off between complexity and performance**.

Ripple carry adders are simpler, but slower. Carry lookahead adders are faster but more complex.

A 4-bit carry-lookahead adder circuit

# A 4-bit **carry-lookahead** adder circuit

#### What information is needed? Where? How?

speed vs. complexity tradeoffs ~ the "cs facets" of engineering

What's the <u>other half</u> of computation?

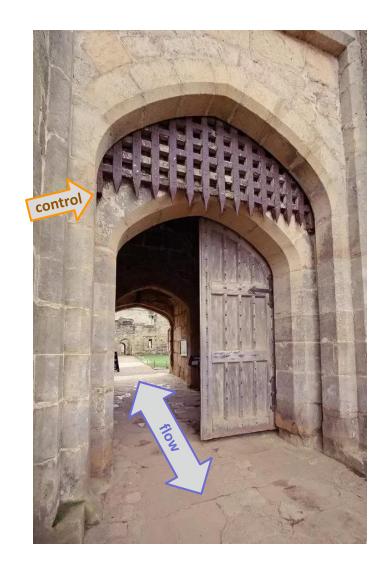

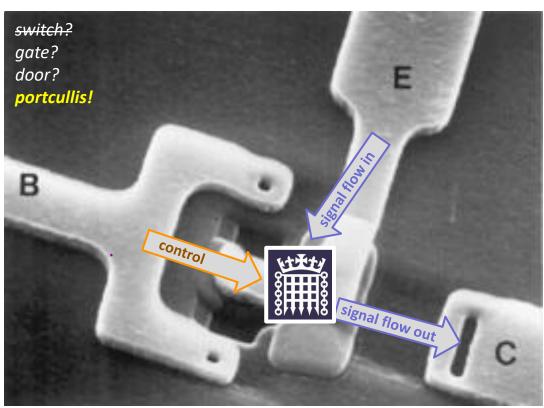

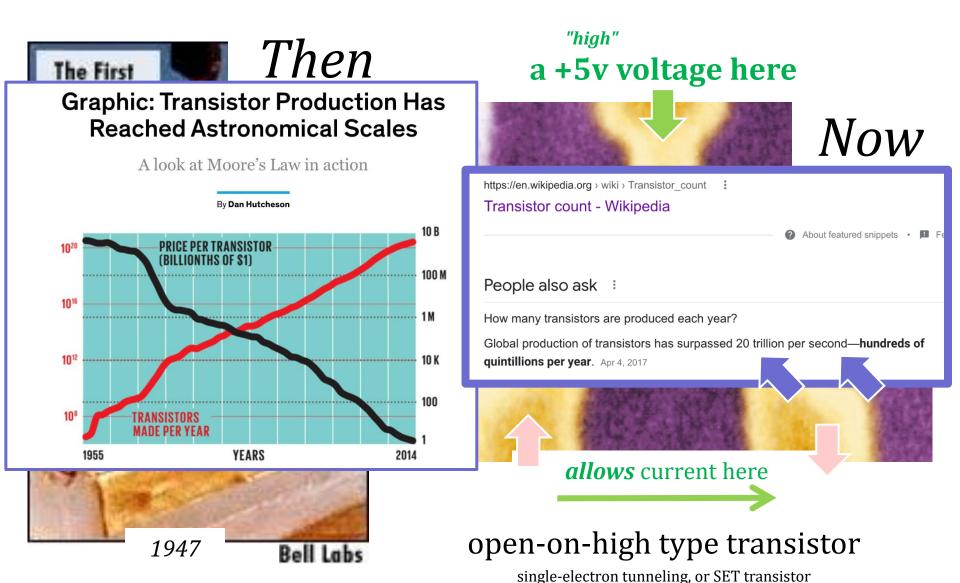

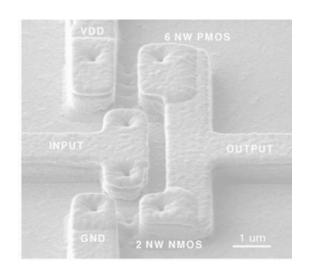

# Today's gates?

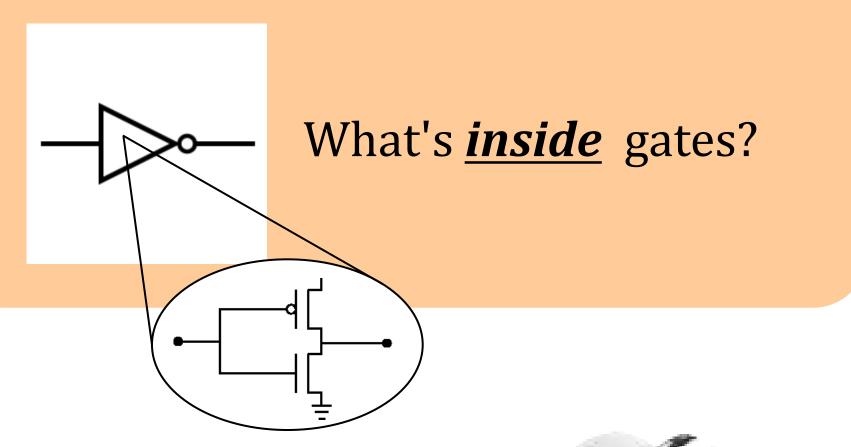

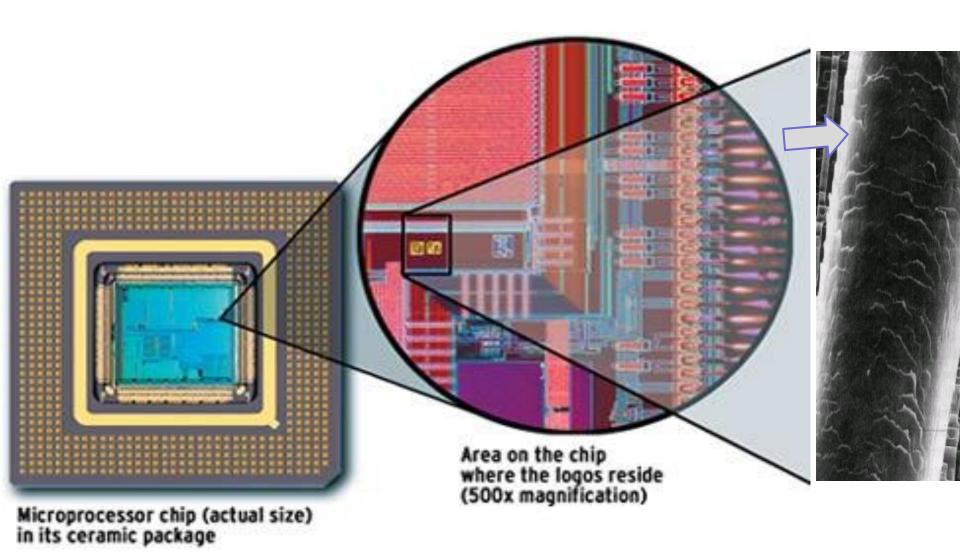

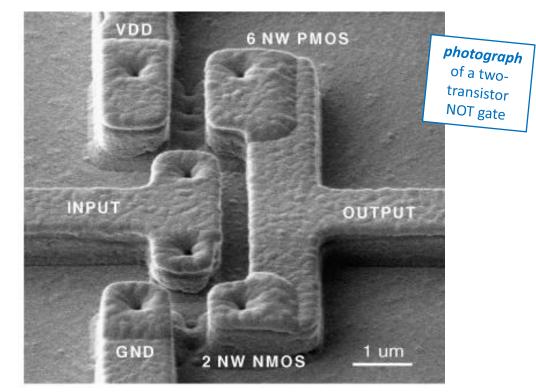

#### are from silicon-based switches ~ *transistors*

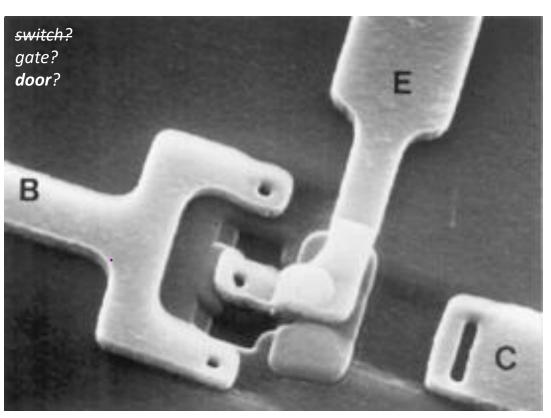

switches?

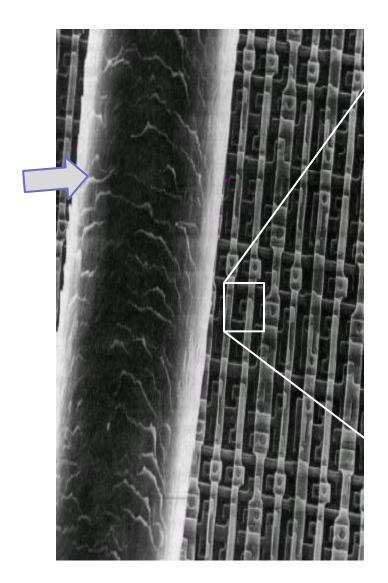

a single etched transistor labeled with base (b), emitter (e), and collector (c)

#### are from silicon-based switches ~ *transistors*

a single etched transistor labeled with base (b), emitter (e), and collector (c)

#### **One** transistor!

#### **One** transistor!

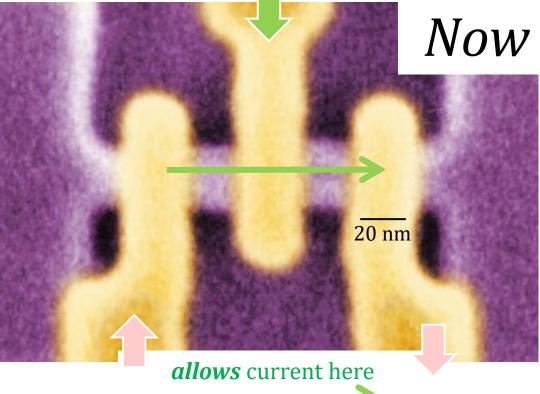

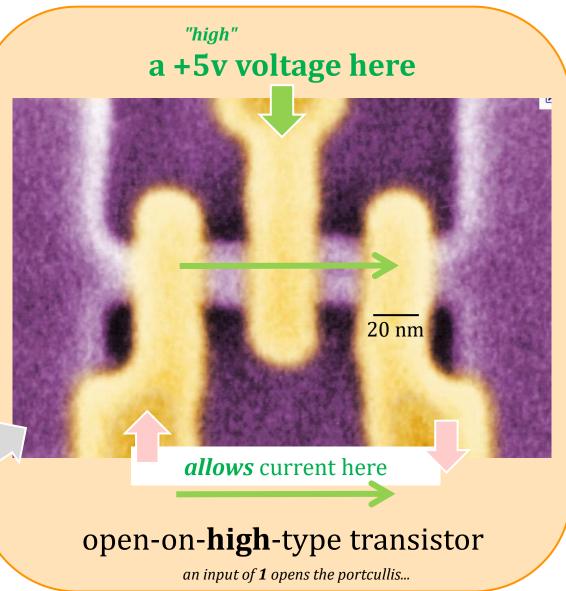

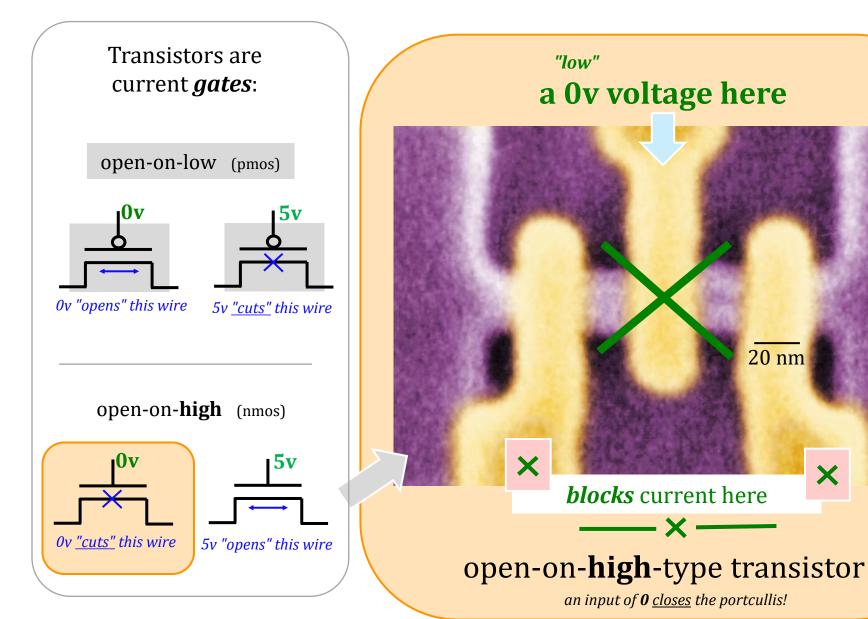

"high"

a +5v voltage here

open-on-high type transistor

single-electron tunneling, or SET transistor

# Lots of transistors!

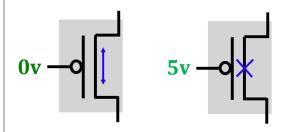

# Two types of transistors...

# Two types of transistors...

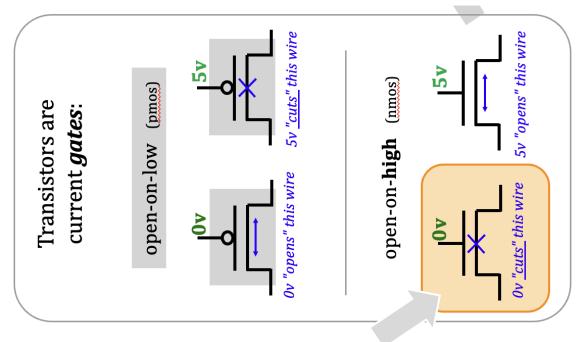

#### Rotations are common...

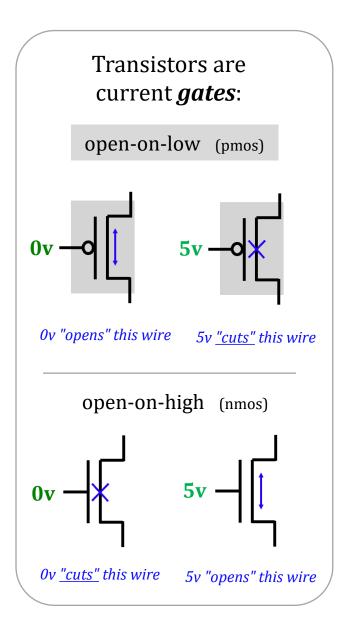

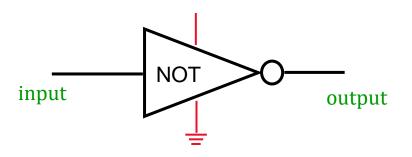

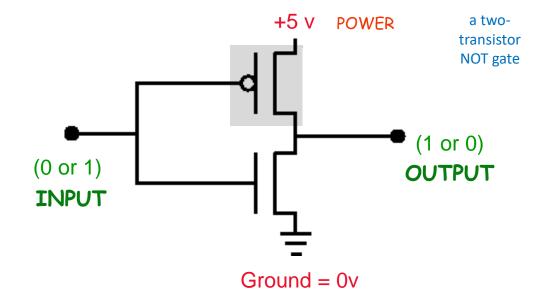

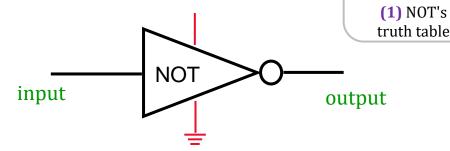

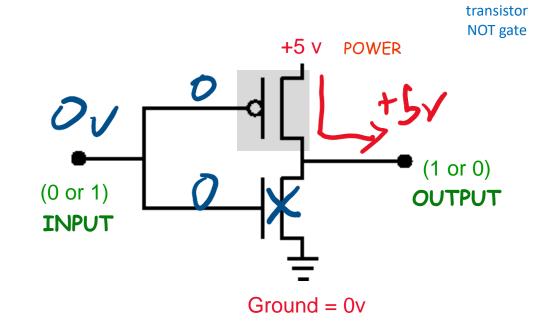

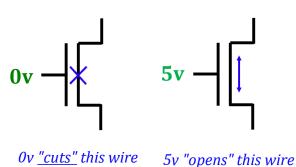

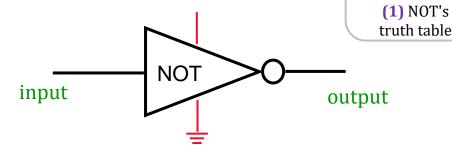

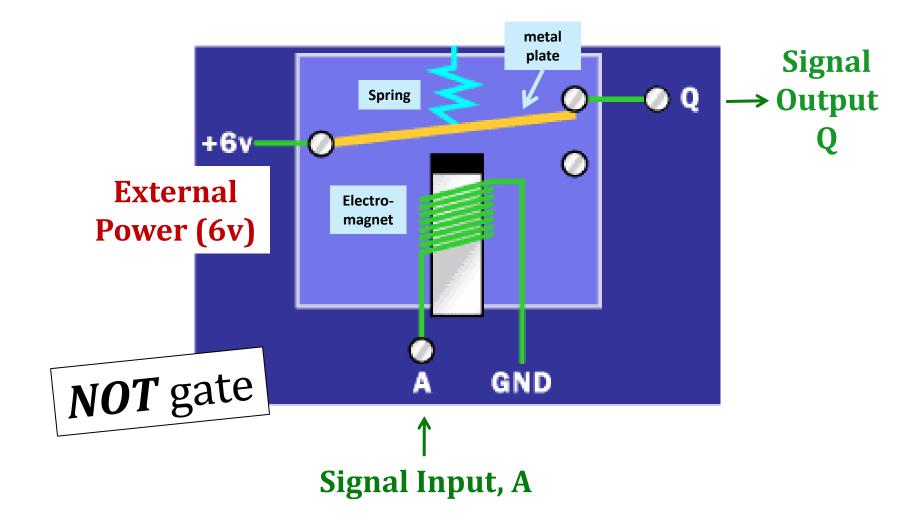

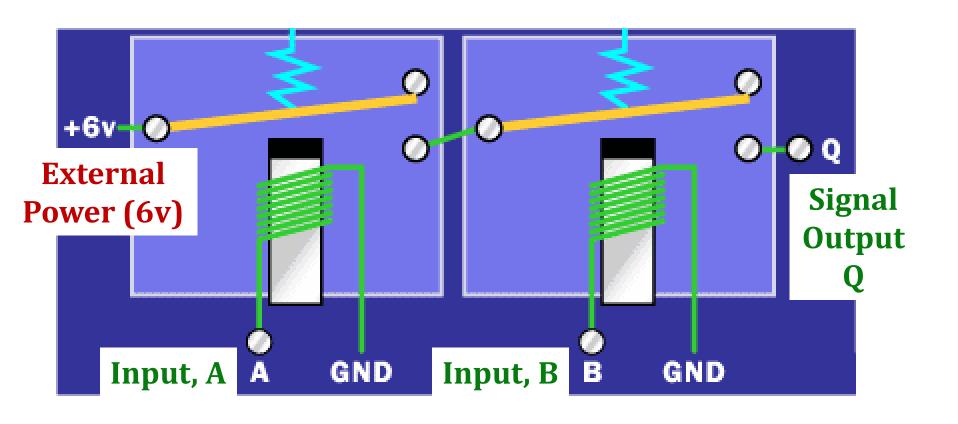

### Building a NOT gate

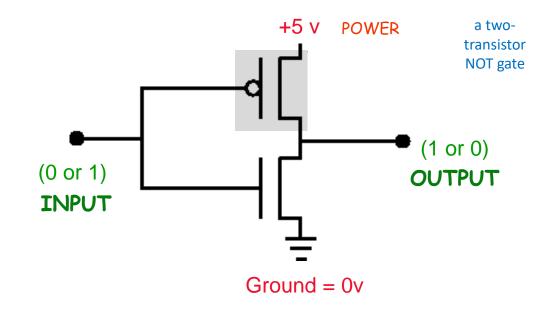

Building a **NOT** gate from transistors:

### a NOT gate

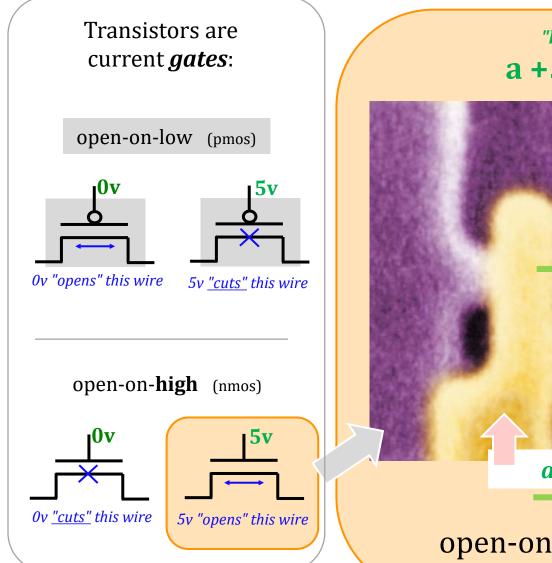

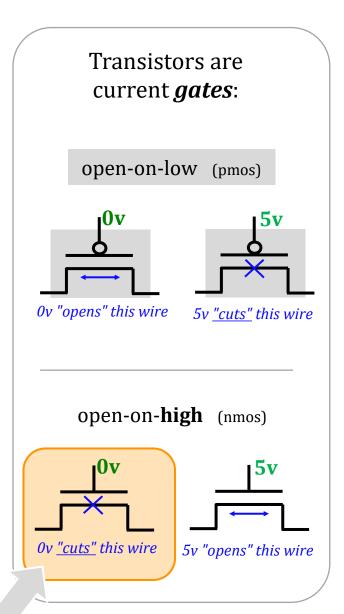

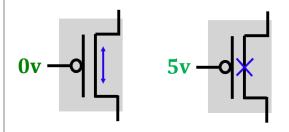

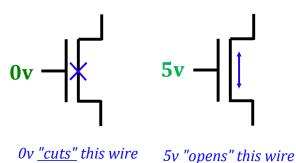

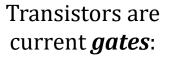

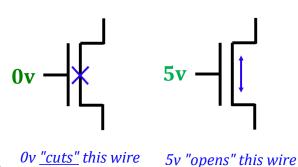

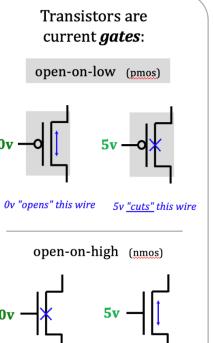

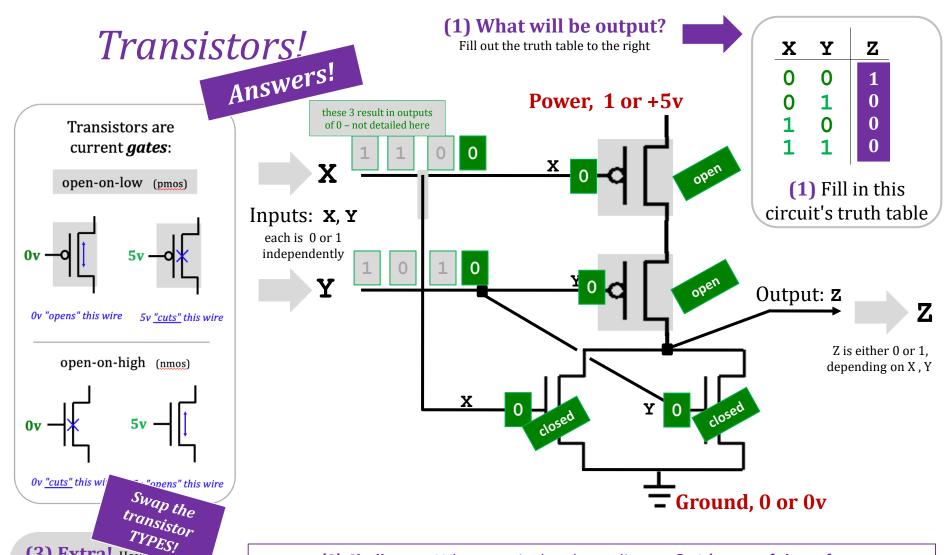

Transistors are current *gates*:

open-on-low (pmos)

Ov "opens" this wire 5v "cuts" this wire

open-on-high (nmos)

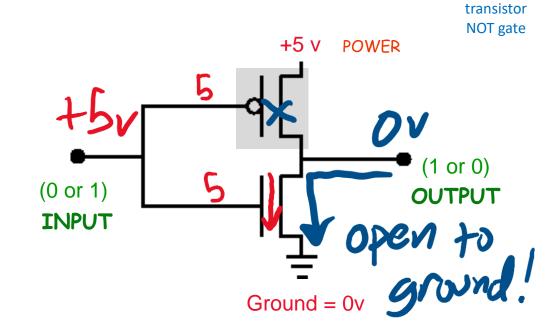

## Building a NOT gate

In Out

0 1

1 0

a two-

open-on-low (pmos)

0v "opens" this wire 5v "cuts" this wire

open-on-high (nmos)

#### Building a **NOT** gate from transistors:

## Building a NOT gate

In Out

0 1

1 0

a two-

open-on-low (pmos)

Ov "opens" this wire 5v "cuts" this wire

open-on-high (nmos)

Building a **NOT** gate from transistors:

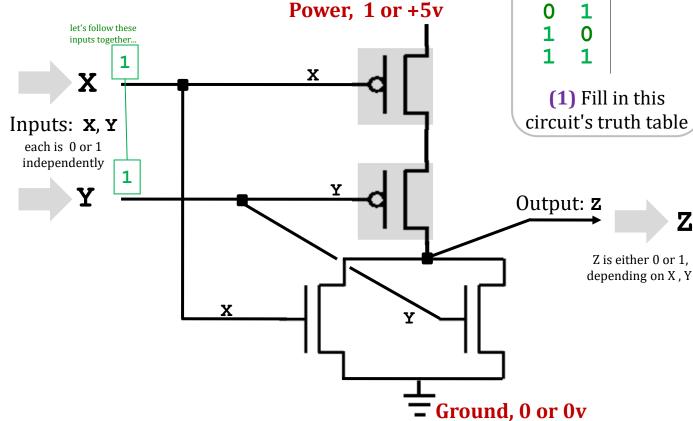

#### **Transistors!**

(1) What will be output?

Fill out the truth table to the right

5v "opens" this wire

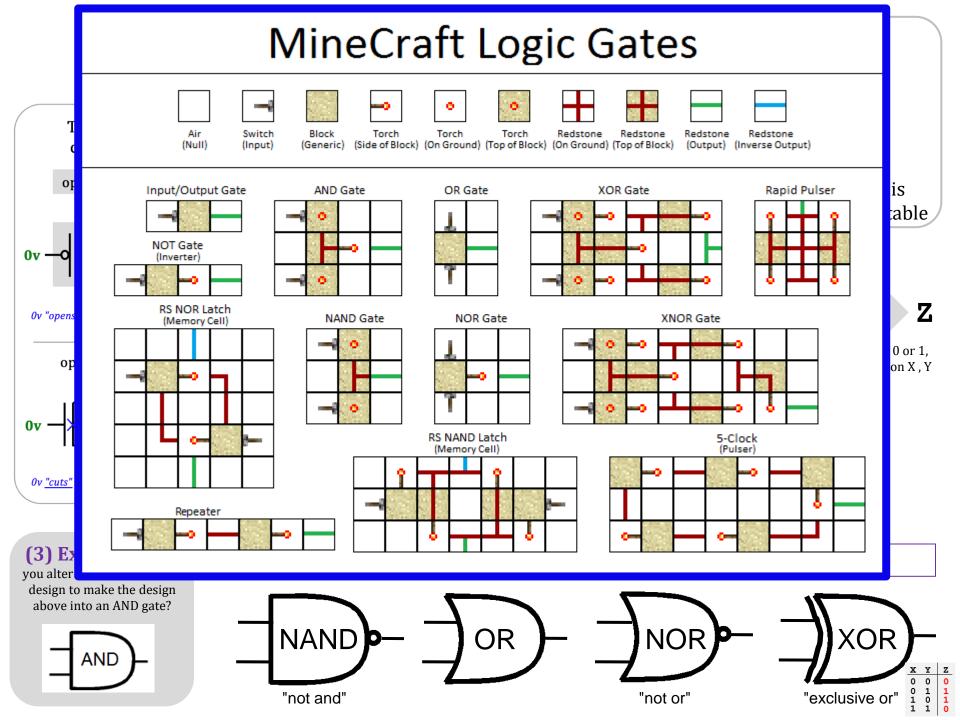

(3) Extra! How could you alter the transistor-level design to make the design above into an AND gate?

Ov "cuts" this wire

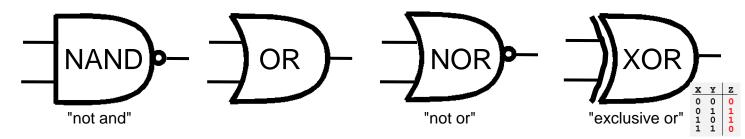

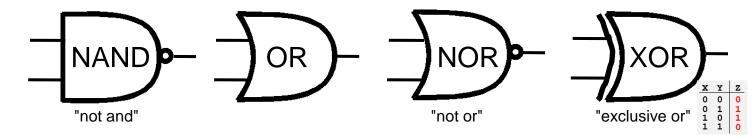

(2) Challenge: What gate is the above diagram? It's one of these four:

(3) Extra! How co.

you alter the transistor-level design to make the design above into an AND gate?

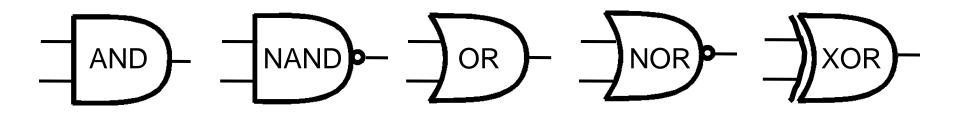

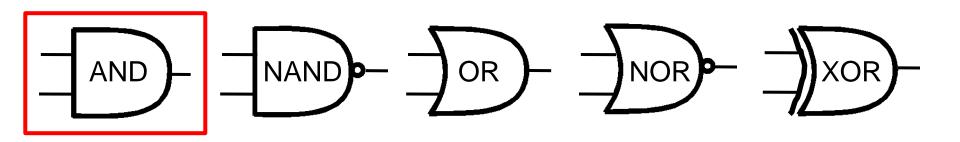

AND

(2) Challenge: What gate is the above diagram? It's one of these four:

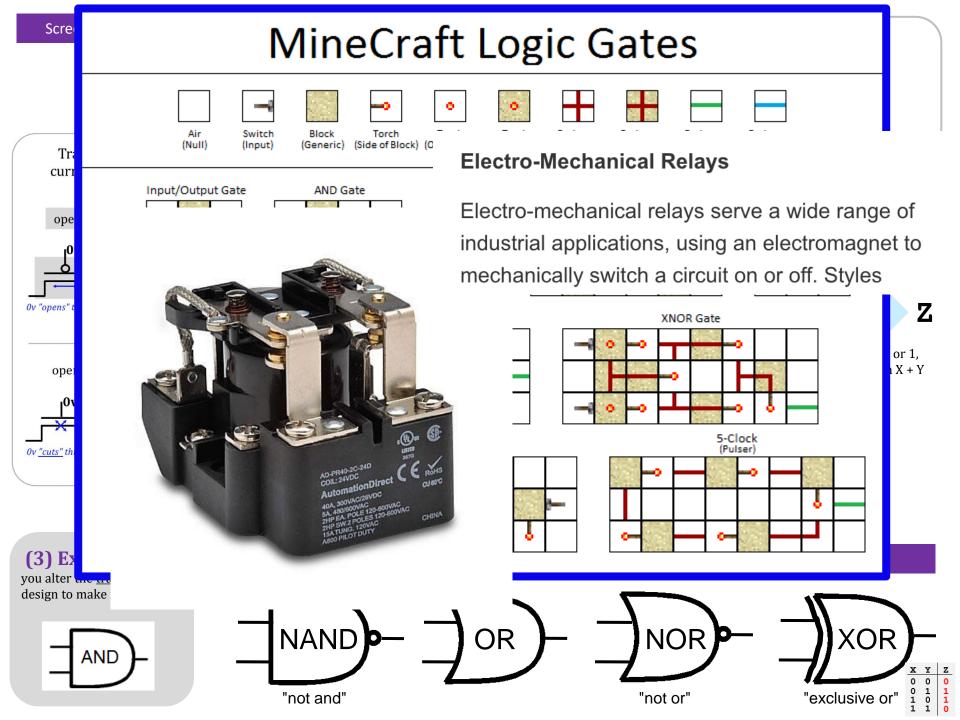

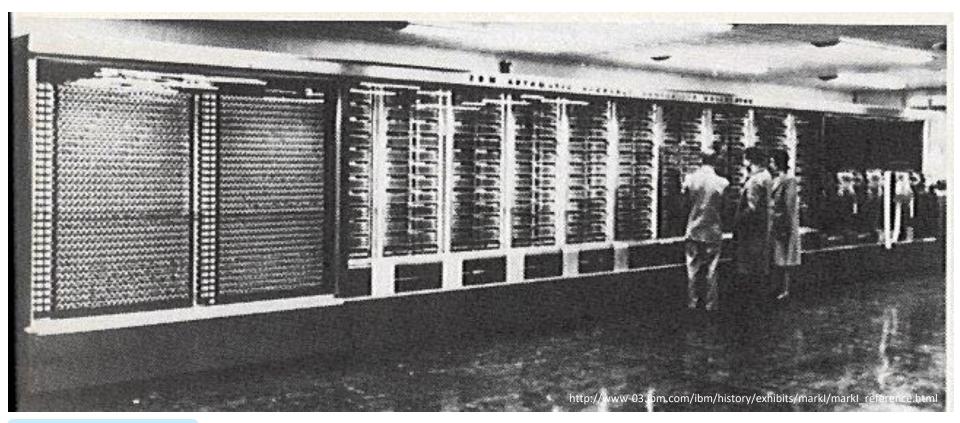

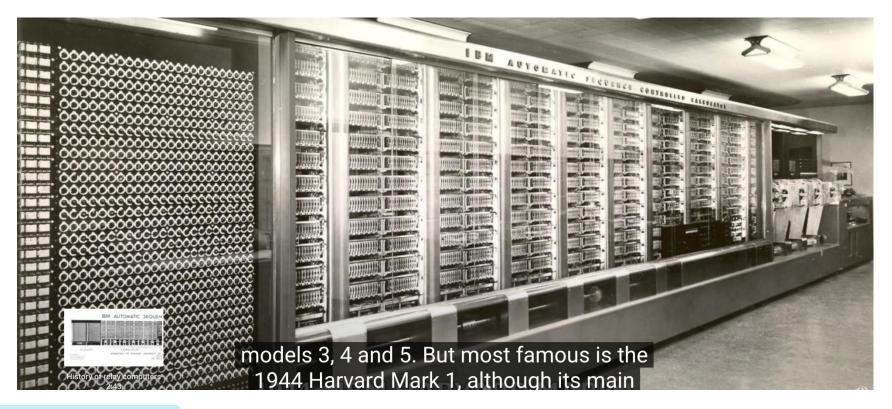

### Their Mark 1

an early, relay-based computer

Grace Hopper + Howard Aiken, Harvard ~ 1944

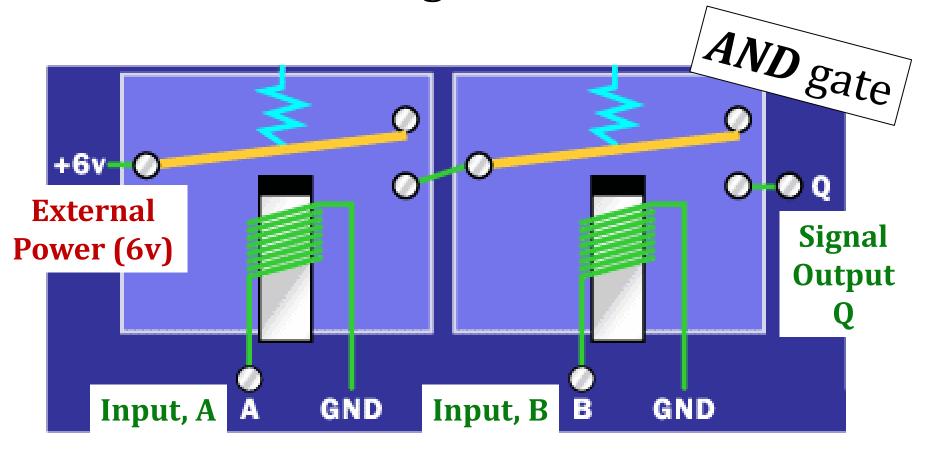

## Electromechanical "gates" (relays)

1940's computers

### Which gate is this?

Which gate is this?

### Their Mark 1

#### an early, relay-based computer

Grace Hopper + Howard Aiken, Harvard ∼ 1944

ran at 0.00001 MHz

5 tons530 miles of wiring765,299 distinct parts!

Addition: **0.6 seconds**

Multiplication: **5.7 seconds**

Division: **15.3 seconds**

## Our Mark 1?

an "early," quantum-based computer

### Transistors as disruptive technology

#### point contact transistor

copyright: Lucent / Bell Lab

1947: **Bell Labs**

seeking better amplifiers for phone lines

team of physicists: W. Brattain, W. Shockley, and J. Bardeen

1948: junction transistor

much more robust design

1956: Shockley Semiconductor Co.

in hometown of Palo Alto...

in a few months...

the "traitorous eight" left to found

1957: Fairchild Semiconductor Co.

... and so begins the valley's siliconization

### What's *inside* gates?

What's the <u>other half</u> of computation?

## Half a computer: the CPU

transistors

gates

arithmetic

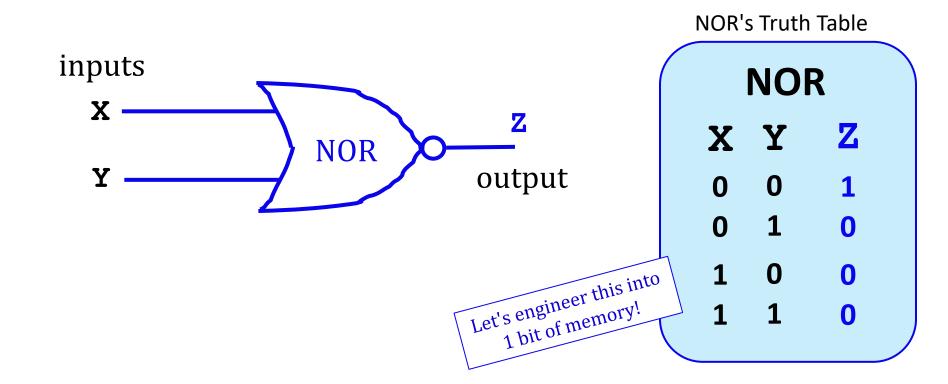

# For systems, a face-lift is to add an edge that *creates a cycle*, not just an additional node.

- also Alan Perlis

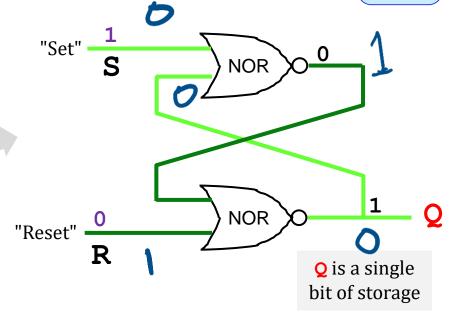

• The circuit starts with R being 0 + S being 0

and **Q** starts at \_0\_

the "loopback wire" from S to R will be 1

What if **S** stays **0** and **R** is set to **1**?

**Q** is then set to \_\_\_

\_0\_

What happens if S stays 0 and R is set back to 0?

**Q** still stays (!) at \_\_\_

0

What happens if R is 0 and S is set to 1?

**Q** is then set to

\_1\_

What happens if S is 0 and R is set back to 0?

**Q** still stays (!) at

1

Why does "S" stand for "Set" and R for "Reset"?

S "sets" Q to 1; R "resets" it back to 0.

Memory!

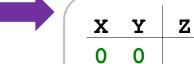

X Y Z

0 0 1

0 1 0

1 0 0

1 1 0

NOR's Truth Table

**NOR**

Take a look at this circuit:

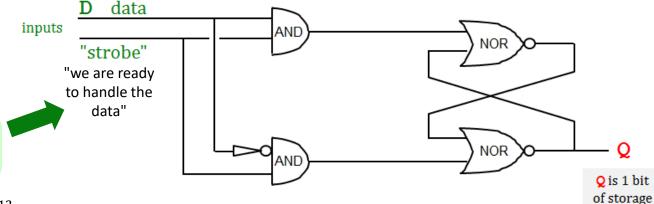

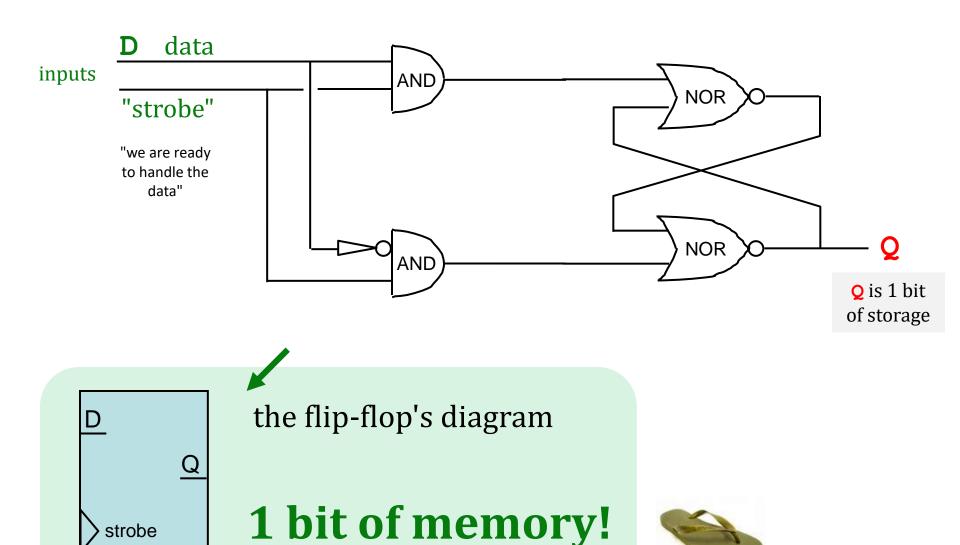

The D (data) line holds a single bit we want to store (either a 0 or a 1).

How does the strobe bit help store the bit D into Q?

**Hint**: What happens when the "strobe" is 1?

## The flip-flop

# The flip-flop

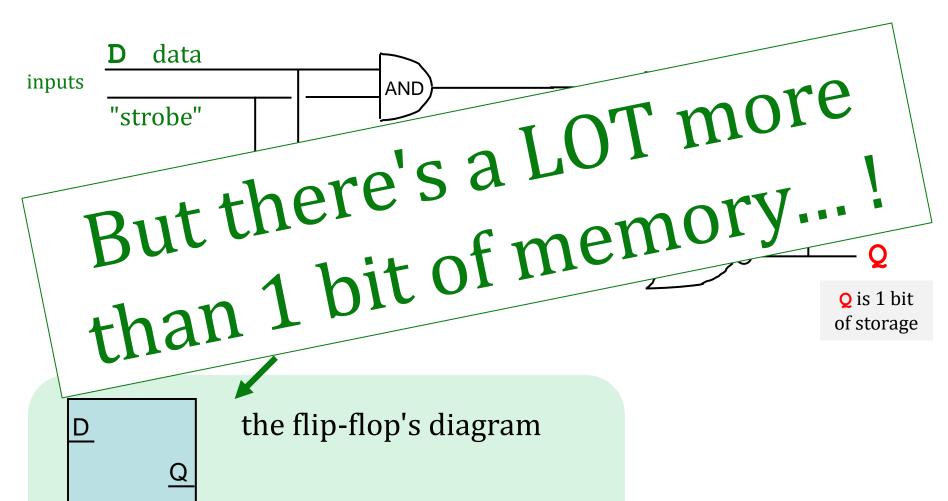

1 bit of memory!

strobe

# Random Access Memory

- 3 bits stored at location 00

- 3 bits stored at location 01

- 3 bits stored at location 10

- 3 bits stored at location 11

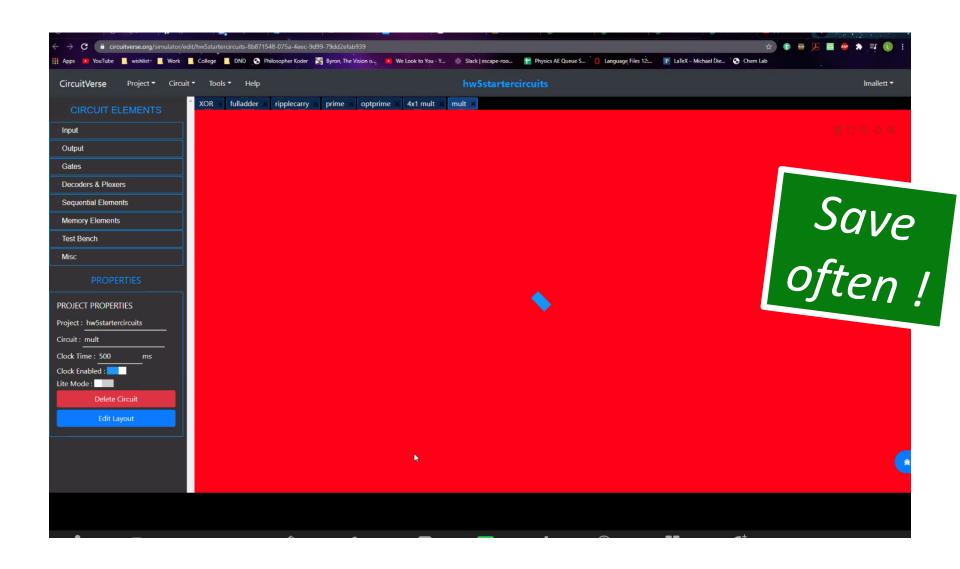

Happy Wiring!

And happy October'ing!